EN Disk er en enhet som lagrer (og noen ganger viser) antall ganger en bestemt hendelse eller prosess har skjedd, ofte i forhold til et klokkesignal. Tellere brukes i digital elektronikk for telleformål, de kan telle spesifikke hendelser som skjer i kretsen. For eksempel, i UP-teller øker en teller tellingen for hver stigende flanke av klokken. Ikke bare teller, en teller kan følge den bestemte sekvensen basert på designen vår som en hvilken som helst tilfeldig sekvens 0,1,3,2... De kan også designes ved hjelp av flip-flops. De brukes som frekvensdelere der frekvensen til gitt pulsbølgeform er delt. Tellere er sekvensielle kretser som teller antall pulser kan være enten i binær kode eller BCD-form. Hovedegenskapene til en teller er timing, sekvensering og telling. Telleren fungerer i to moduser

Opp disk

Ned teller

Motklassifisering

Tellere er grovt sett delt inn i to kategorier

- Asynkron teller

- Synkronteller

1. Asynkron teller

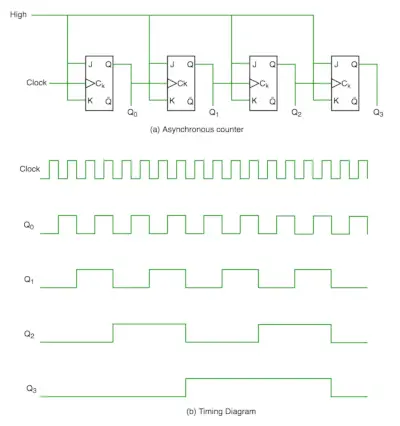

I asynkron teller bruker vi ikke universell klokke, bare første flip-flop er drevet av hovedklokken og klokkeinngangen til resten av den påfølgende flip-floppen er drevet av output fra tidligere flip-flop. Vi kan forstå det ved å følge diagram-

Det er tydelig fra tidsdiagrammet at Q0 endrer seg så snart den stigende flanken til klokkepulsen påtreffes, Q1 endres når den støtende flanken av Q0 påtreffes (fordi Q0 er som klokkepuls for andre flipflop) og så videre. På denne måten genereres krusninger gjennom Q0,Q1,Q2,Q3, derfor kalles det også RIPPLE teller og seriell teller. En rippelteller er et kaskadearrangement av flip flops der utgangen fra en flip flop driver klokkeinngangen til den følgende flip flop

2. Synkronteller

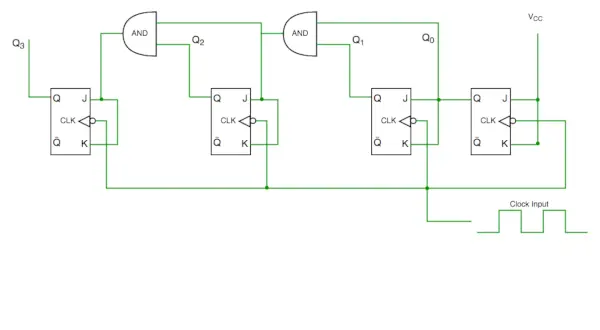

I motsetning til den asynkrone telleren, har den synkrone telleren én global klokke som driver hver flip-flop slik at utgangen endres parallelt. Den ene fordelen med synkron teller fremfor asynkron teller er at den kan operere på høyere frekvens enn asynkron teller, da den ikke har kumulativ forsinkelse på grunn av samme klokke som gis til hver flip flop. Det kalles også som parallellteller.

Synkron tellerkrets

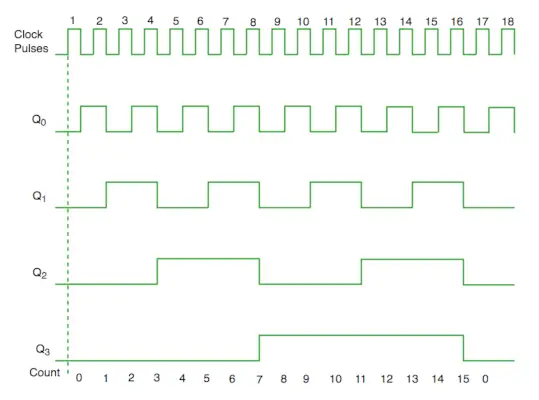

Tidsdiagram synkron teller

Fra kretsdiagram ser vi at Q0-bit gir respons på hver fallende flanke av klokken mens Q1 er avhengig av Q0, Q2 er avhengig av Q1 og Q0, Q3 er avhengig av Q2,Q1 og Q0.

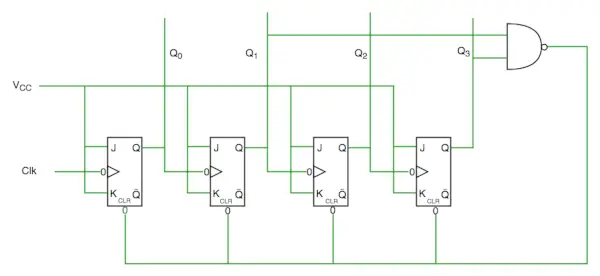

Tiår Counter

En tiårteller teller ti forskjellige tilstander og tilbakestilles deretter til utgangstilstandene. En enkel tiår teller vil telle fra 0 til 9, men vi kan også gjøre tiår tellere som kan gå gjennom alle ti tilstander mellom 0 til 15 (for 4 bit teller).

| Klokkepuls | Q3 | Q2 | Q1 | Q0 |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 |

| 10 | 0 | 0 | 0 | 0 |

Sannhetstabell for enkel tiårteller

Tiår teller kretsdiagram

Vi ser fra kretsdiagrammet at vi har brukt nand-port for Q3 og Q1 og mater denne for å slette inngangslinjen fordi binær representasjon av 10 er—

1010

Og vi ser at Q3 og Q1 er 1 her, hvis vi gir NAND av disse to bitene for å slette input, vil telleren være klar ved 10 og igjen starte fra begynnelsen.

Viktig poeng : Antall flip flops brukt i telleren er alltid større enn lik ( Logg2n ) hvor n=antall tilstander i telleren.

Noen tidligere års gatespørsmål på tellere

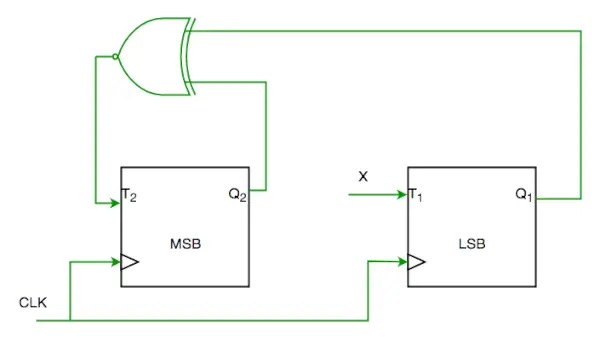

Q1. Vurder den delvise implementeringen av en 2-bits teller ved å bruke T flip-flops etter sekvensen 0-2-3-1-0, som vist nedenfor

For å fullføre kretsen, bør inngangen X være

(A) Q2?

(B) Q2 + Q1

(C) (Q1? Q2)'

(D) Q1 ? Q2 (GATE-CS-2004)

Løsning:

Fra krets ser vi

T1=XQ1’+X’Q1—-(1)

OG

T2=(Q2 ? Q1)'—-(2)

OG ØNSKET UTSTYR ER 00->10->11->01->00

SÅ BØR X VÆRE Q1Q2'+Q1'Q2 TILFREDS 1 OG 2.

SÅ ANS ER (D) DEL.

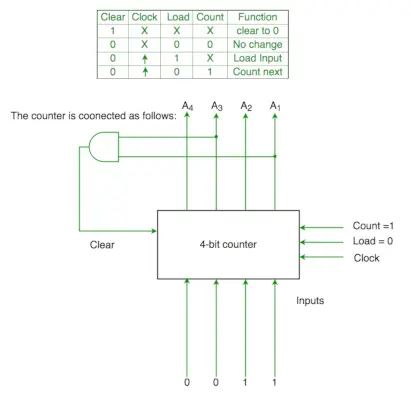

Q2. Kontrollsignalfunksjonene til en 4-bits binær teller er gitt nedenfor (der X er ikke bryr seg)

Telleren kobles til som følger:

Anta at telleren og gateforsinkelsene er ubetydelige. Hvis telleren starter på 0, går den gjennom følgende sekvens:

(A) 0,3,4

(B) 0,3,4,5

(C) 0,1,2,3,4

(D) 0,1,2,3,4,5 (GATE-CS-2007)

Løsning:

Opprinnelig A1 A2 A3 A4 =0000

Clr=A1 og A3

Så når A1 og A3 begge er 1, går den igjen til 0000

Derfor 0000(init.) -> 0001(A1 og A3=0)->0010 (A1 og A3=0) -> 0011(A1 og A3=0) -> 0100 ( A1 og A3=1 )[ klar tilstand tilfredsstilt] ->0000(init.) så den går gjennom 0->1->2->3->4

Ans er (C) del.

hvordan konvertere heltall til streng java

Quiz om digital logikk

Artikkel bidratt av Anuj Batham,