Flip-flop er et begrep som kommer under digital elektronikk, og det er en elektronisk komponent som brukes til å lagre én enkelt informasjonsbit.

Diagrammatisk representasjon av flip flop

- Siden flip flop er en sekvensiell krets er inngangen basert på to parametere, den ene er den nåværende inngangen og den andre er utgangen fra den forrige tilstanden.

- Den har to utganger, begge komplementerer hverandre.

- Det kan være i en av to stabile tilstander, enten 0 eller 1.

Grunnleggende diagram av flip flop

Hva er T Flip Flop?

- T flip flop eller for å være presis er kjent som Toggle Flip Flop fordi den kan veksle utgangen avhengig av inngangen.

- T her står for Veksle .

- Toggle indikerer i utgangspunktet at biten vil bli snudd, dvs. enten fra 1 til 0 eller fra 0 til 1.

- Her tilføres en klokkepuls for å betjene denne floppen, derfor er det en klokket flip-flop.

Konstruksjon av T Flip Flop

Vi kan konstruere T flip på tre måter, nemlig:

- Ved å bruke SR Flip Flops.

- Ved å bruke D Flip Flops.

- Ved å bruke JK Flip Flops

Måter å konstruere T Flip Flop

La oss se konstruksjonen av T Flip Flop ved å bruke SR Flip Flops, som krever 2 AND-porter og 2 NOR-porter som vist nedenfor:

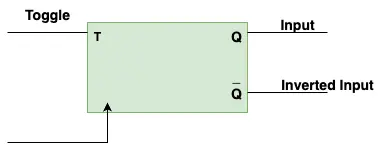

Grunnleggende blokkdiagram av T Flip Flop

Her inneholder blokkdiagram Toggle og klokkeinnganger, Q og Q’ er de komplementerte inngangene.

Arbeid av T Flip Flop

Sak 1 : La oss si, T = 0 og klokkepuls er høy dvs. 1, da vil utgangen fra begge, OG-port 1, OG-port 2 være 0 , port 3 utgang vil være Q og lignende port 4 utgang vil være Q’ så begge verdiene til Q og Q' er de samme som deres forrige verdi, som betyr Hold-tilstand .

Tilfelle 2 : La oss si, T=1 , da vil utgangen av både OG-port 1 være (T * klokke * Q) , og siden T og klokke begge er 1, vil utgangen til OG-port 1 være Q , og tilsvarende utgang fra OG-port 2 vil være (T * klokke * Q') dvs., Q’ . Nå vil gate 3-utgang være (Q'+Q)' og la oss si at Q' er null, så vil gate 3-utgang være (0+Q)’ som betyr Q’ og tilsvarende port 4-utgang vil være (Q+Q’)’ og siden Q' er null, vil port 4-utgang være Q' som betyr 0 ettersom Q' er null. Derfor kan vi i dette tilfellet si at utgangen veksler, fordi T=1 .

Truth Table of T Flip Flop

- Her er T Toggle-inngangen, Q er nåværende tilstandsinngang, Qt+1 er neste tilstandsutgang.

- Herfra kan vi se at når Toggle (T) er 0, er neste tilstandsutgang (Qt+1) den samme som gjeldende tilstandsinngang (Q).

- Når Toggle (T) er 1, vil neste tilstandsutgang (Qt+1) være et komplement til gjeldende tilstandsinngang (Q), noe som betyr at den veksles.

Karakteristisk ligning

- Den karakteristiske ligningen forteller oss om hva som vil være den neste tilstanden til flip flop når det gjelder nåværende tilstand.

- For å få den karakteristiske ligningen, er K-Map konstruert som vil bli vist som nedenfor:

- Hvis vi løser ovennevnte K-Map, vil den karakteristiske ligningen være Q(n+1) = TQn’ + T’Qn = T XOR Qn

Eksitasjonstabell

Eksitasjonstabell forteller i utgangspunktet om eksitasjonen som kreves av flip flop for å gå fra gjeldende tilstand til neste tilstand.

- Her, når T er 0, er Qt+1 det samme som input Q.

- Og når T er 1, er Qt+1 kompliment til inngang Q.

Bruk av T Flip Flop

Det er mange bruksområder for T Flip Flop i Digital System, som er oppført nedenfor:

- Tellere : T Flip Flops brukt i disker. Tellere teller antall hendelser som skjer i et digitalt system.

- Datalagring : T Flip Flops brukes til å lage minne som brukes til å lagre data når strømmen er slått av.

- Synkrone logiske kretser : T flip-flops kan brukes til å implementere synkrone logiske kretser, som er kretser som utfører operasjoner på binære data basert på et klokkesignal. Ved å synkronisere logikkkretsens operasjoner til klokkesignalet ved hjelp av T-flip-flops, kan kretsens oppførsel gjøres forutsigbar og pålitelig.

- Frekvensinndeling : Den brukes til å dele frekvensen til et klokkesignal med 2. Flip-flop vil bytte utgang hver gang klokkesignalet går over fra høyt til lavt eller lavt til høyt, og deler derfor klokkefrekvensen med 2.

- Skiftregistre : T flip-flops kan brukes i skiftregistre som brukes til å skifte binære data i én retning.

Konklusjon

I denne artikkelen tar vi utgangspunkt i det grunnleggende om flip-flops, at hva som faktisk er flip-flops, og så diskuterte vi om T-flip-flops, tre to måter vi kan konstruere T-flip-flops på, det er Basic Block Diagram, Working of T Flip Flops , det er sannhetstabellen, karakteristisk ligning så vel som eksitasjonstabellen, og til slutt diskuterte vi bruken av T-flip-flops.